模拟CMOS集成电路仿真设计基础 共漏跟随器及其在集成电路设计中的关键作用

在模拟CMOS集成电路设计中,共漏跟随器(Common-Drain Configuration),常被称为源极跟随器(Source Follower),是一种基础而重要的单级放大器结构。它不仅作为电压缓冲器,还在信号链中扮演着阻抗变换与电平位移的关键角色。本文将深入探讨其基本工作原理、关键特性,并结合仿真设计基础,阐述其在集成电路设计中的应用。

一、共漏跟随器基本结构与工作原理

共漏跟随器采用NMOS或PMOS晶体管实现。以NMOS为例,其基本结构为:信号从栅极输入,从源极输出,漏极直接连接至电源VDD(或通过一个电流源/电阻)。因此,输入与输出共享漏极节点,故称“共漏”。其核心功能是提供一个高输入阻抗、低输出阻抗的电压缓冲。输出电压Vout近似等于输入电压Vin减去晶体管的栅源电压VGS,即Vout ≈ Vin - VGS。由于VGS相对恒定(在特定偏置电流下),输出电压能紧密“跟随”输入电压的变化,但存在一个直流电平偏移。

二、关键特性分析

- 电压增益:理想情况下,源极跟随器的电压增益略小于1,通常为0.8至0.95,具体取决于晶体管的跨导gm和源极看到的负载阻抗。增益公式为Av ≈ gm Rout / (1 + gm Rout),其中Rout是输出节点的等效电阻。

- 输入与输出阻抗:高输入阻抗是其突出优点,主要由栅极的极高直流阻抗决定,使其易于从前级高阻抗节点获取信号。输出阻抗较低,约为1/gm,这使得它能够驱动重负载(如低阻抗线路或容性负载),减少负载效应。

- 频率响应:由于输出节点通常存在较大容性负载,其频率响应受输出极点限制。但因其简单的结构,通常能提供相对较宽的带宽。

- 线性度:在合理偏置下,源极跟随器能提供良好的线性度,但大信号摆幅可能因VGS变化引入非线性失真。

三、仿真设计基础与实践考量

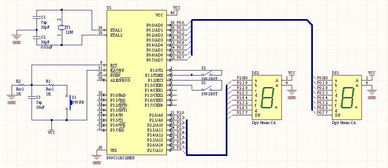

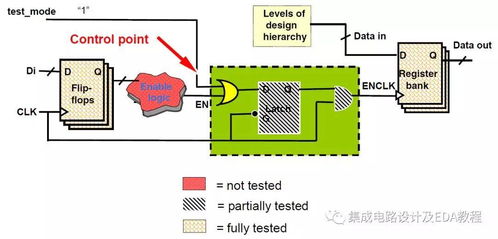

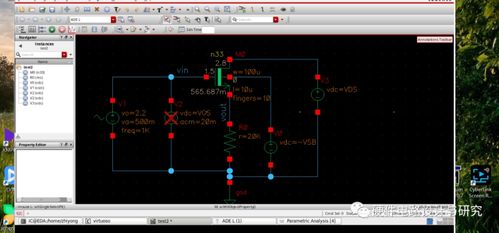

在现代集成电路设计流程中,仿真至关重要。设计共漏跟随器时,需通过仿真软件(如Cadence Spectre, HSPICE等)进行多维度验证:

- 直流工作点仿真:确保晶体管处于饱和区,以获得稳定的VGS和偏置电流。这是电路正常工作的基础。

- 交流小信号仿真:测量电压增益、输入/输出阻抗、频率响应(带宽、相位裕度)等。需注意,仿真应包含所有寄生电容和电阻模型,以反映实际芯片性能。

- 瞬态仿真:评估大信号行为,包括压摆率、建立时间、输出摆幅以及线性度(通过THD分析)。特别要关注电平位移是否在系统允许范围内。

- 噪声仿真:分析电路的噪声贡献,特别是热噪声和闪烁噪声,这对于高精度模拟系统尤为重要。

- 工艺角与蒙特卡洛分析:考虑工艺偏差、温度变化对性能的影响,确保设计在各类条件下均稳健可靠。

四、在集成电路设计中的应用

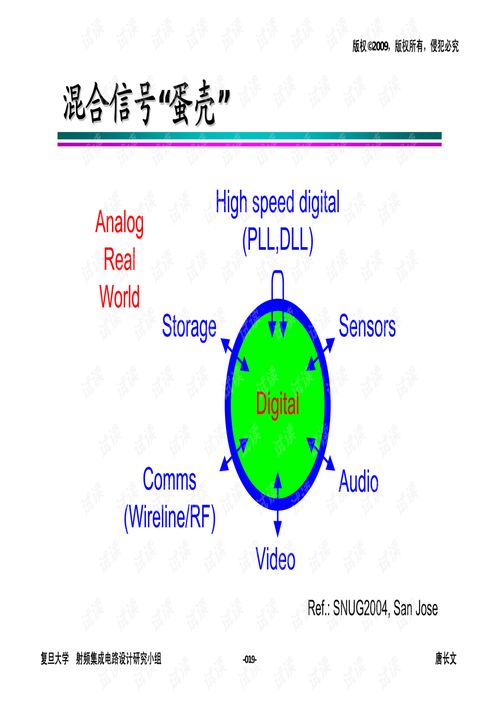

共漏跟随器广泛应用于各类模拟与混合信号系统中:

- 电压缓冲:隔离高阻抗信号源与低阻抗负载,防止负载效应导致的信号衰减。

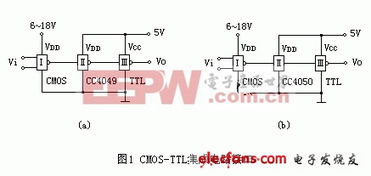

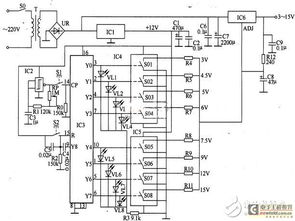

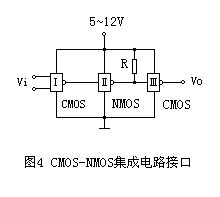

- 电平位移:在不同电压域之间平移直流电平,例如在低压核心电路与更高电压的I/O接口之间。

- 输出驱动:作为最后一级驱动,直接驱动片外负载或长互连线。

- 参考电压产生:利用其稳定的VGS降,生成一个比电源电压低VGS的参考电压。

设计时需权衡:增益损失、输出摆幅限制(受VGS和过驱动电压影响)、功耗(由偏置电流决定)以及面积(晶体管尺寸和可能的偏置电路)。采用互补结构(如推挽式源极跟随器)可以改善摆幅和驱动能力。

共漏跟随器是模拟CMOS设计工具箱中的基石。通过深入理解其原理并结合严谨的仿真验证,设计师能够有效地将其集成到复杂系统中,实现可靠的信号调理与接口功能,从而构建出高性能、高鲁棒性的集成电路。

如若转载,请注明出处:http://www.datiantongchen.com/product/66.html

更新时间:2026-02-25 22:03:24